一键发布任务

发布成功

发布成功

赞赏金额:

支付金额:5元

支付方式:

赞赏成功!

你的赞赏是对作者最大的肯定~?

什么是时序逻辑电路

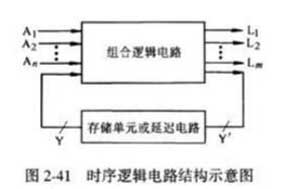

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

时序逻辑电路的设计(一)

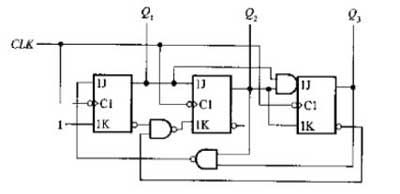

下图的时序逻辑电路是:设计一个串行数据检测器,对它的要求是:连续输入3个或3个以上的1时输出为1,其他输入情况下输出为0。

时序逻辑电路的设计(二)

下图的时序逻辑电路是:试用JK触发器和门电路设计一个同步七进制计数器

时序逻辑电路的设计(三)

下图的时序逻辑电路是:设计一“011”序列检测器,每当输入011码时,对应最后一个1,电路输出为1

时序逻辑电路是数字逻辑电路的重要组成部分,时序逻辑电路又称时序电路,主要由存储电路和组合逻辑电路两部分组成。它和我们熟悉的其他电路不同,其在任何一个时刻的输出状态由当时的输入信号和电路原来的状态共同决定,而它的状态主要是由存储电路来记忆和表示的。同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路而言,往往具有难度大、电路复杂并且应用范围广的特点。

推荐阅读: